# Announcements

## TA Application Time - Due today

### (No longer optional) ARM Reading linked off labs page ( Look at D.7 and D.8 )

# Traps / Exceptions

Divide by zero

Invalid operation code

Segmentation fault

Reference to invalid page table entry

Syscall

# Exception Handling Approaches

Branch to "fixed" address

- Actually fixed

- Address stored in fixed address (typically low or high addresses in memory).

- Address stored in special register

- Save information including PC where error occurred (like bal saves return address).

- Senter supervisor mode!

## Privileged Modes

Most processors have a register indicating current mode:

- user mode

- supervisor mode

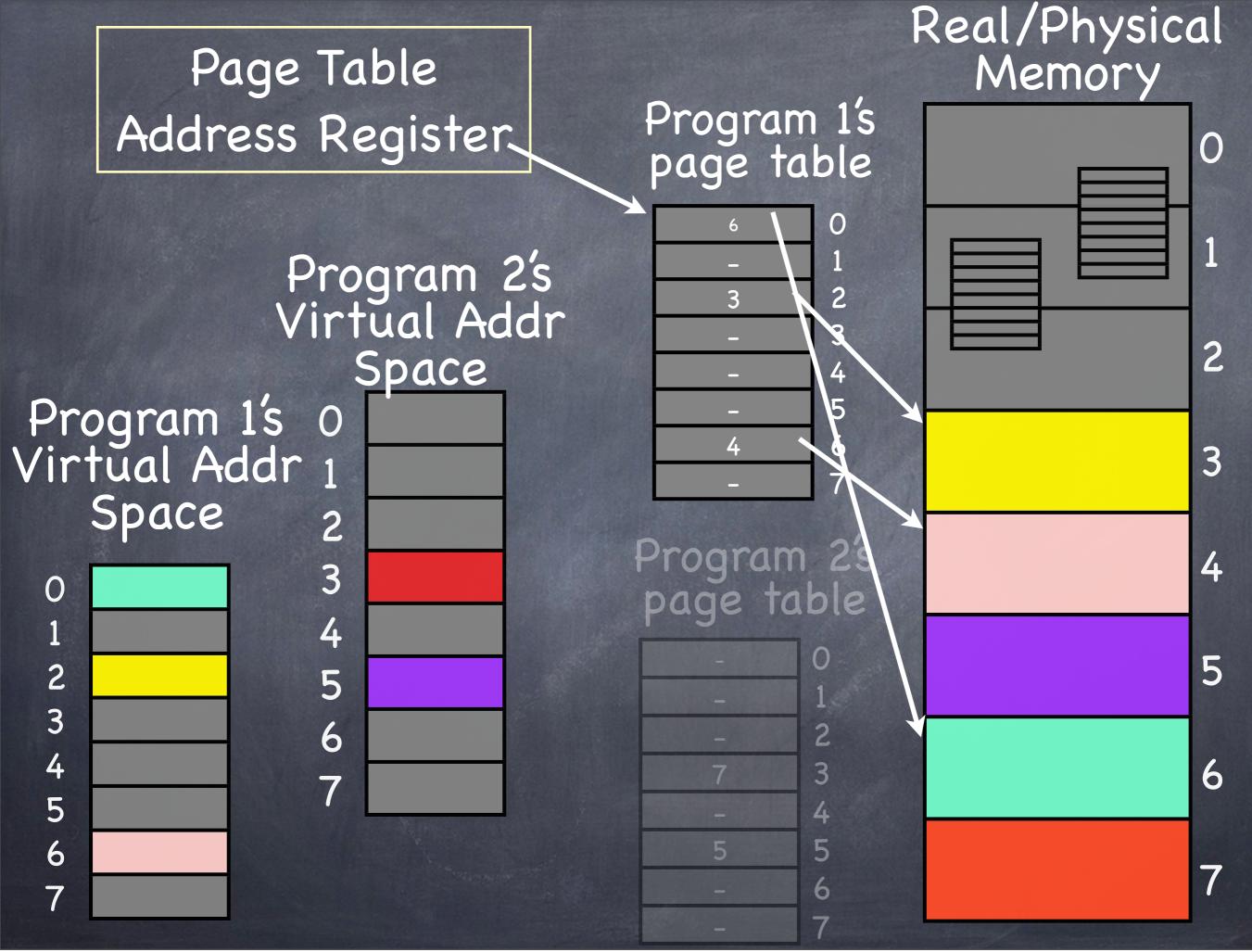

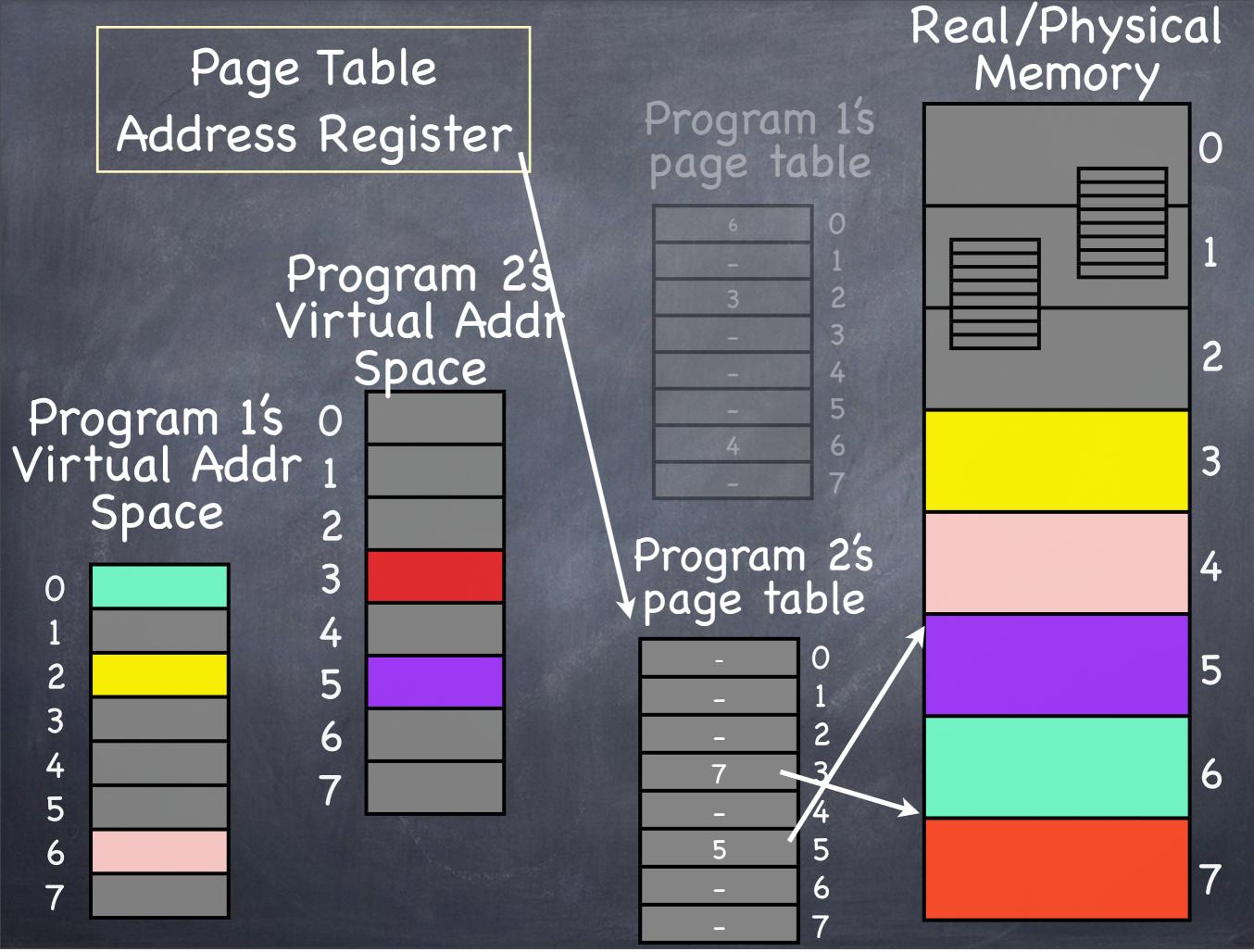

Can only set page table address register in supervisor mode ==> memory protection

Can only set mode register in supervisor mode!

#### ARM1136JF-S<sup>™</sup> and ARM1136J-S<sup>™</sup> Technical Reference Manual Revision: r1p3

#### **2.7.** Operating modes

In all states there are seven modes of operation:

- User mode is the usual ARM program execution state, and is used for executing most application programs

- Fast interrupt (FIQ) mode is used for handling fast interrupts

- Interrupt (IRQ) mode is used for general-purpose interrupt handling

- Supervisor mode is a protected mode for the operating system

- Abort mode is entered after a data or instruction Prefetch Abort

- System mode is a privileged user mode for the operating system

- Undefined mode is entered when an Undefined instruction exception occurs.

Modes other than User mode are collectively known as privileged modes.

#### Table 2-4 Exception vectors

| Exception             | Vector address |

|-----------------------|----------------|

| Reset                 | 0x00000000     |

| Undefined instruction | 0x00000004     |

| SWI                   | 0x0000008      |

| Prefetch Abort        | 0x0000000C     |

| Data Abort            | 0x00000010     |

| Reserved              | 0x00000014     |

| IRQ                   | 0x00000018     |

| FIQ                   | 0x0000001C     |

|                               | All modes |                 |            |           |           |           |  |  |

|-------------------------------|-----------|-----------------|------------|-----------|-----------|-----------|--|--|

| ſ                             | r0        |                 |            |           |           |           |  |  |

|                               | r1        |                 |            |           |           |           |  |  |

|                               | r2        | 15 banked       |            |           |           |           |  |  |

|                               | r3        | general-purpose |            |           |           |           |  |  |

|                               | r4        | registers       |            |           |           |           |  |  |

|                               | r5        |                 |            |           |           |           |  |  |

| 16 general-purpose            | r6        | FIQ mode        |            |           |           |           |  |  |

|                               | r7        | only            | _          |           |           |           |  |  |

| registers                     | r8        | r8_fiq          |            |           |           |           |  |  |

|                               | r9        | r9_fiq          |            |           |           |           |  |  |

|                               | r10       | r10_fiq         |            |           |           |           |  |  |

|                               | r11       | r11_fiq         | Supervisor | Abort     | IRQ       | Undefined |  |  |

|                               | r12       | r12_fiq         | mode only  | mode only | mode only | mode only |  |  |

|                               | r13 (SP)  | r13_fiq         | r13_svc    | r13_abt   | r13_irq   | r13_und   |  |  |

|                               | r14 (LR)  | r14_fiq         | r14_svc    | r14_abt   | r14_irq   | r14_und   |  |  |

|                               | r15 (PC)  |                 |            |           |           |           |  |  |

| rrent Program Status Register | CPSR      | SPSR_fiq        | SPSR_svc   | SPSR_abt  | SPSR_irq  | SPSR_und  |  |  |

Five banked Saved Program Status Registers

Figure 2-1 ARM968E-S register set

Cur

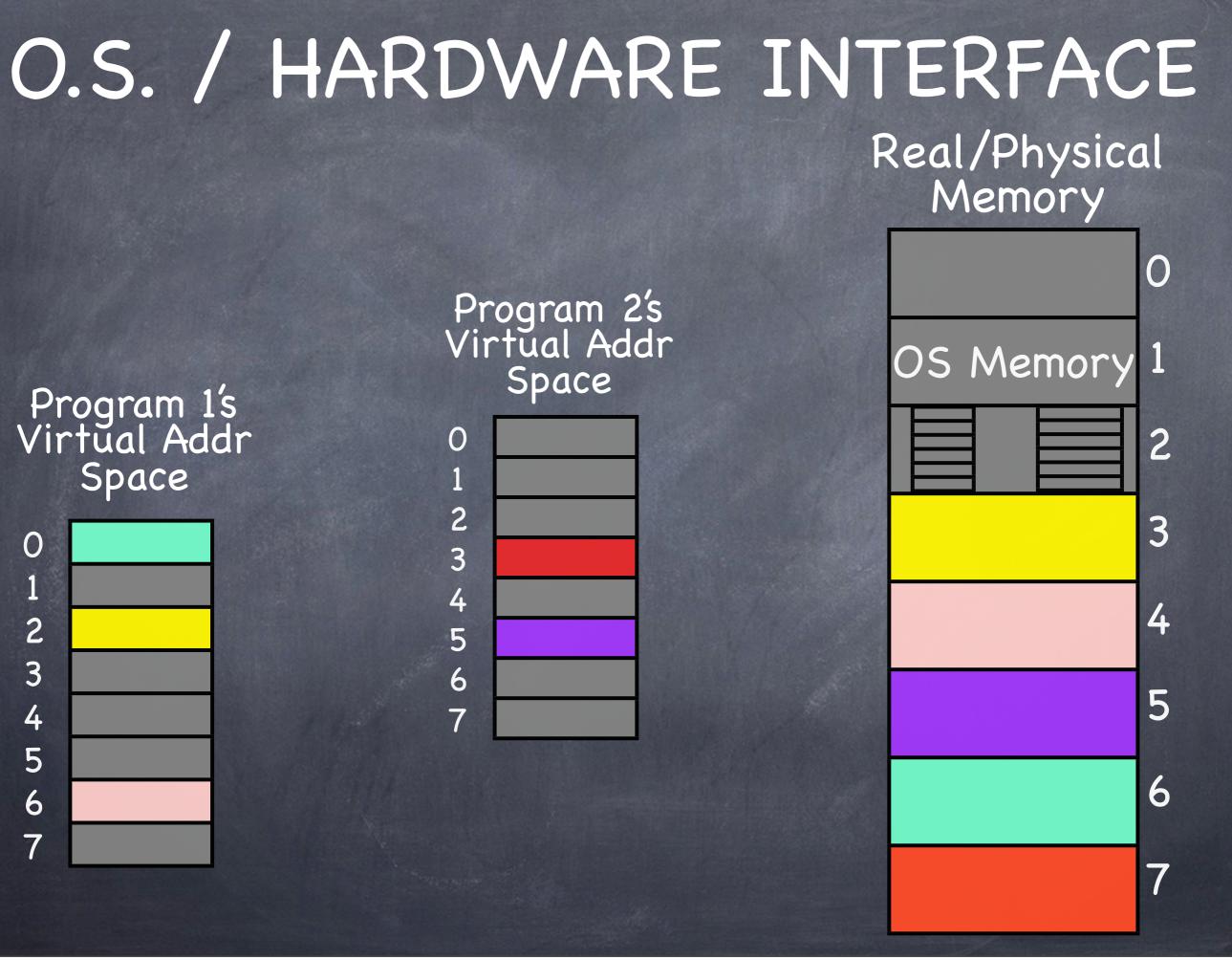

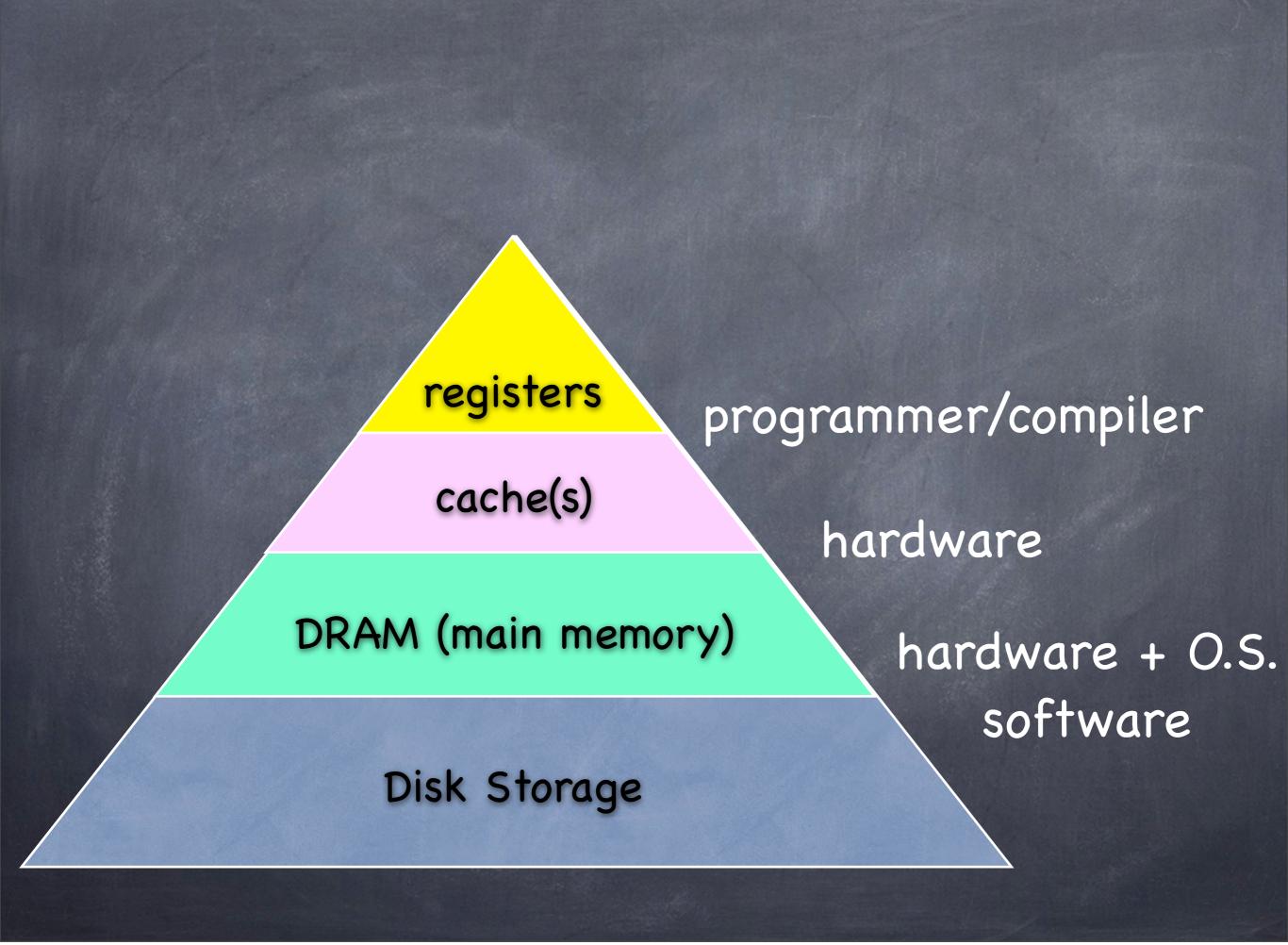

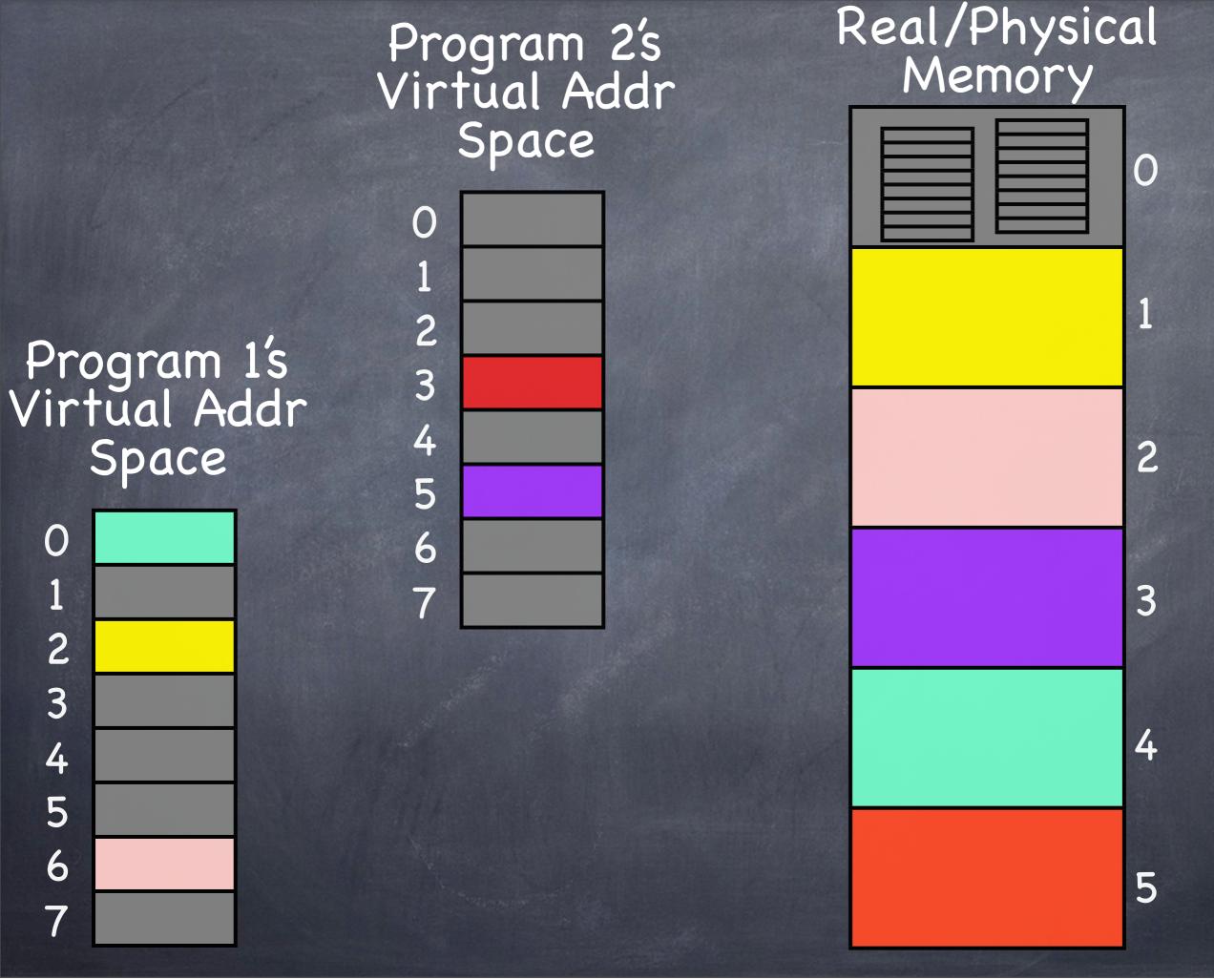

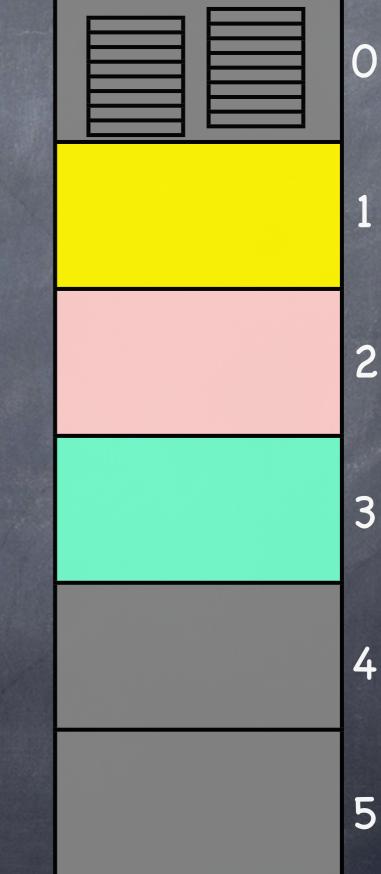

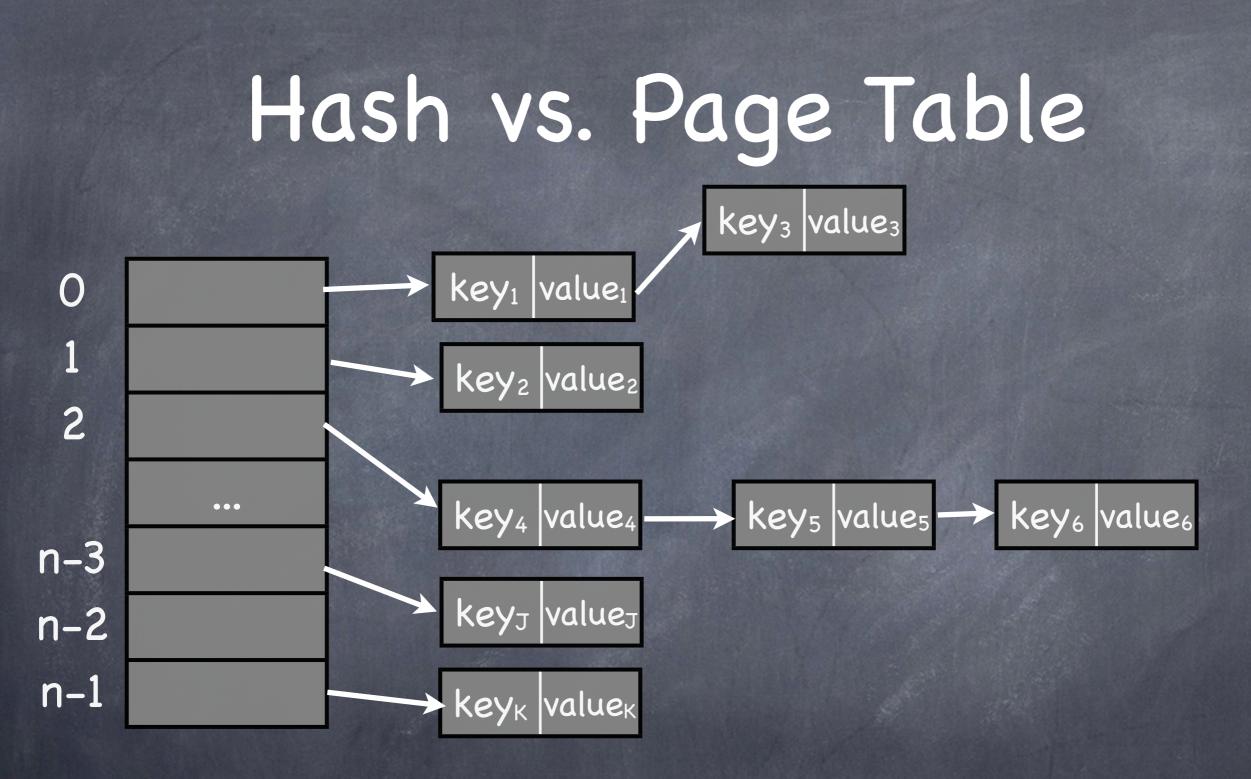

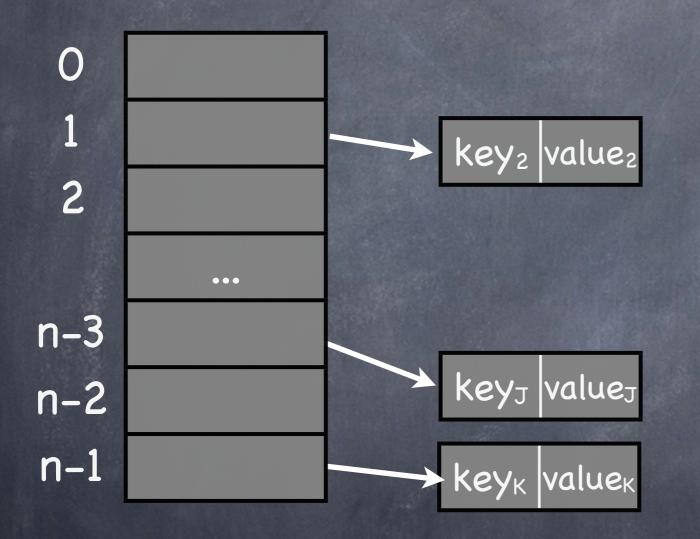

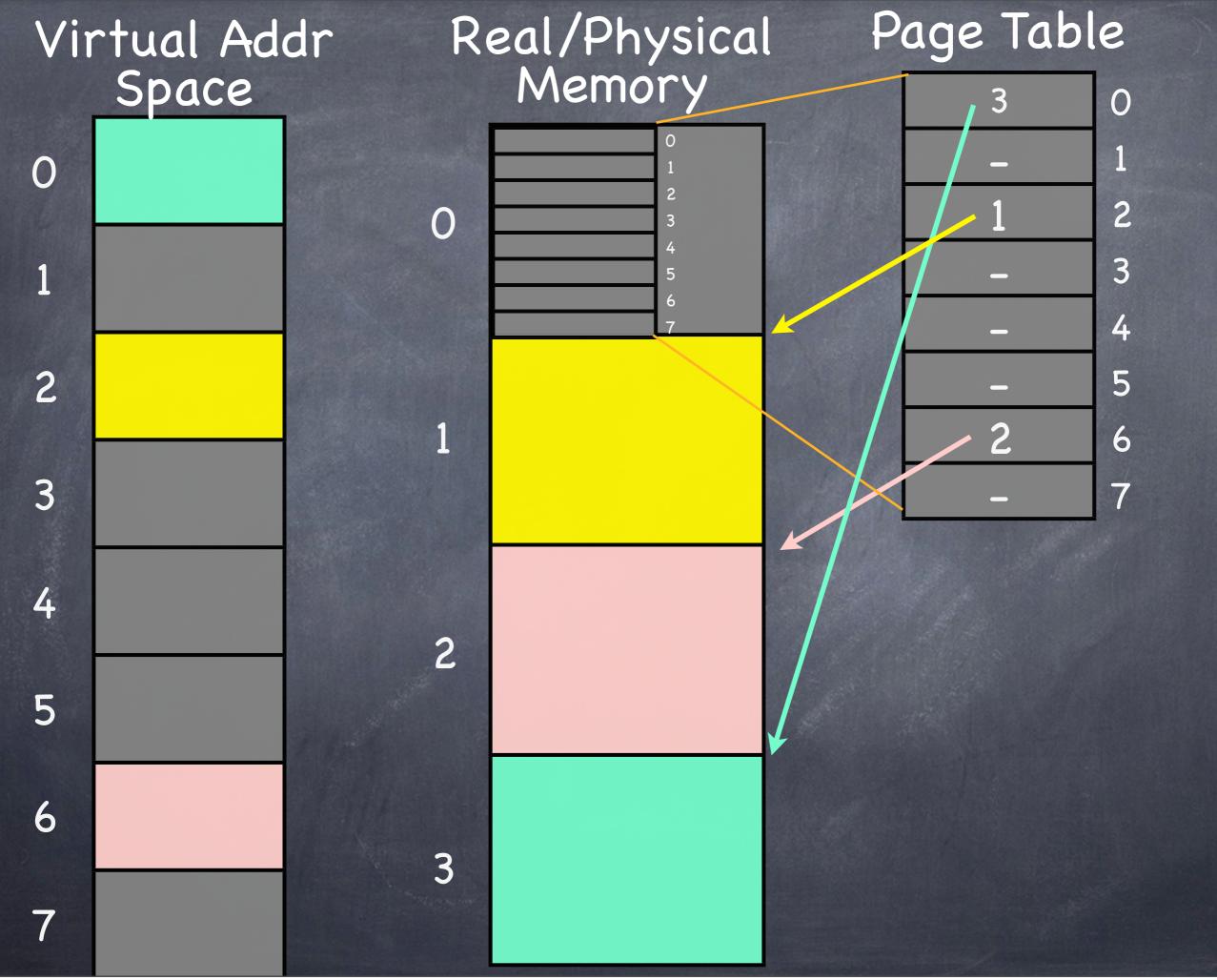

### Program's virtual address space divided into pages

Gray pages in virt. addr. space are stored on disk

Can't afford to traverse chains

Can't afford to discard entries!

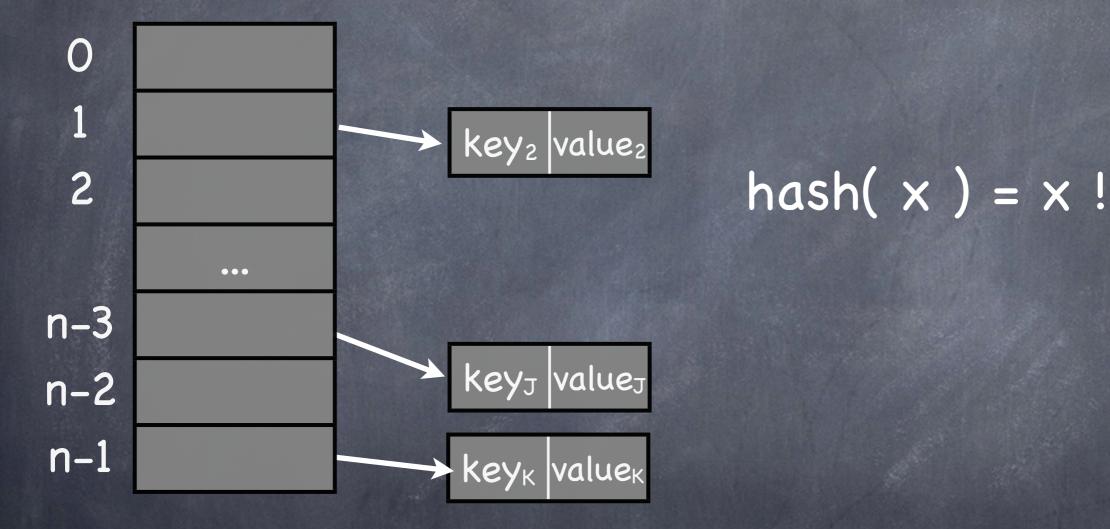

# Sparse Hash = Page Table

$\oslash$  Let n = number of pages in address space

# Sparse Hash = Page Table

$\oslash$  Let n = number of pages in address space

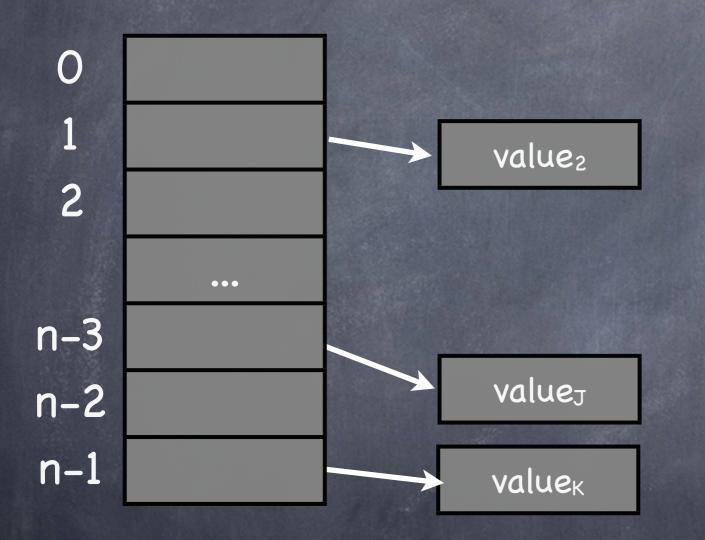

# Sparse Hash = Page Table

Values" in key/value pairs of page table are huge. Can't afford to put them inline.

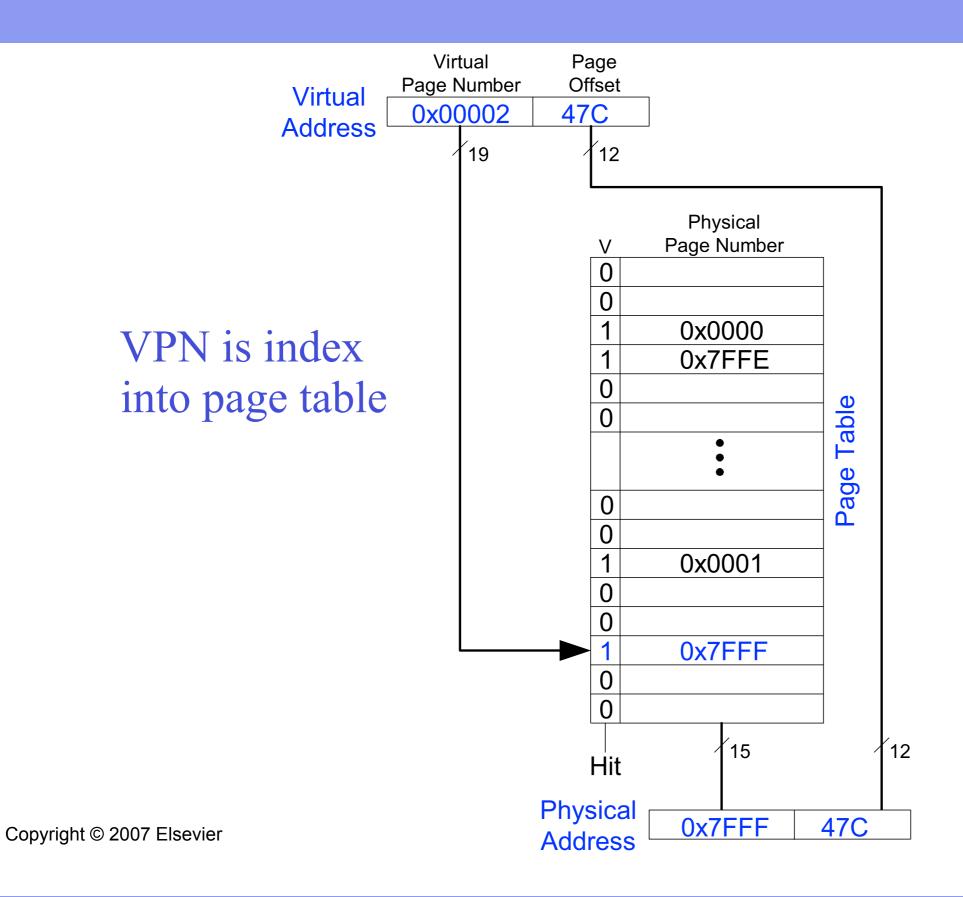

### **Page Table**

8-<>

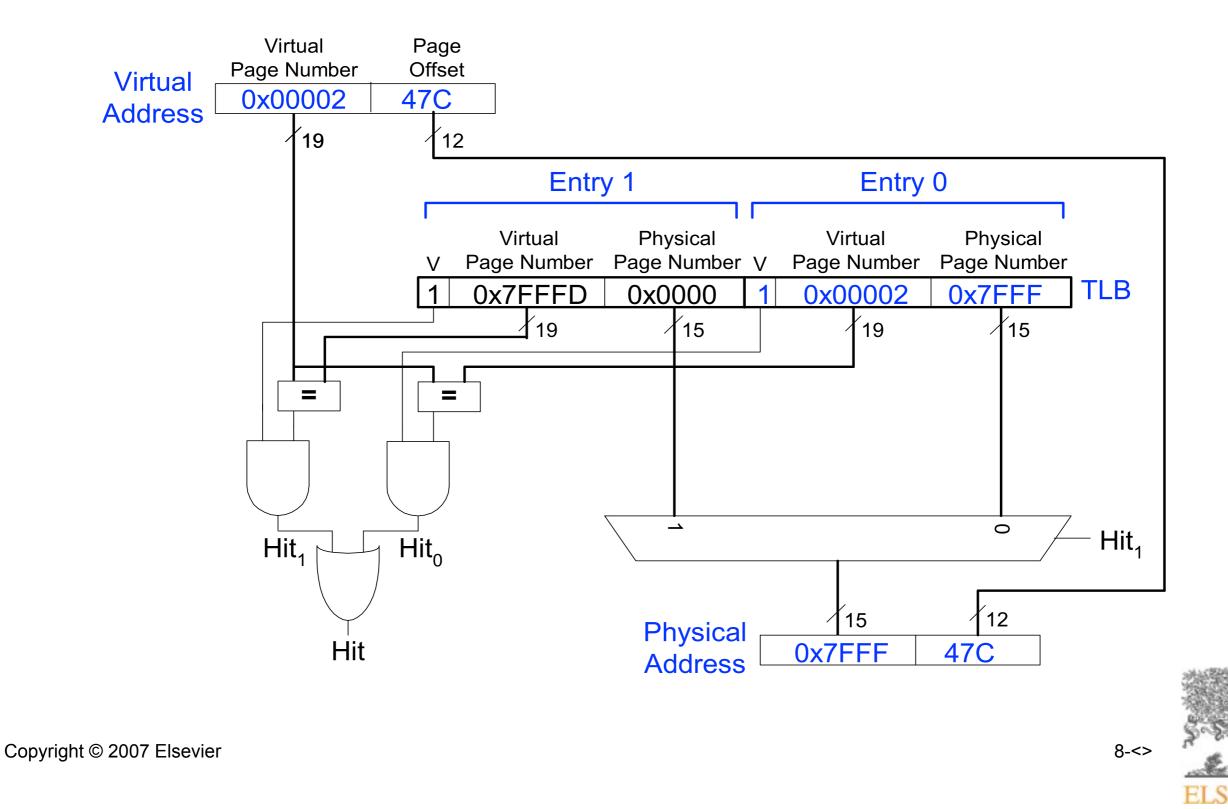

### **Translation Lookaside Buffer (TLB)**

- Page table accesses have a lot of temporal locality

- -Data accesses have temporal and spatial locality

- Large page size, so consecutive loads/stores likely to access same page

- TLB

- -Small: accessed in < 1 cycle

- -Typically 16 512 entries

- -Fully associative

- -> 99 % hit rates typical

- Reduces # of memory accesses for most loads and stores from 2 to 1

8-<>

Copyright © 2007 Elsevier

### **Example Two-Entry TLB**